International Journal of Natural and Engineering Sciences 9 (2): 62-65, 2015 ISSN: 1307-1149, E-ISSN: 2146-0086, www.nobel.gen.tr

# High Performance Memory Management for A Multi-core Architecture (HPMMFMA)

Ahmed MATEEN<sup>1\*</sup> Lareab CHAUDHARY<sup>1</sup> <sup>1</sup>Department of Computer Science, University of Agriculture Faisalabad, Pakistan

| * Corresponding author:       | Received: May 22, 2015  |

|-------------------------------|-------------------------|

| Email: ahmedmatin@hotmail.com | Accepted: 03 July, 2015 |

### Abstract

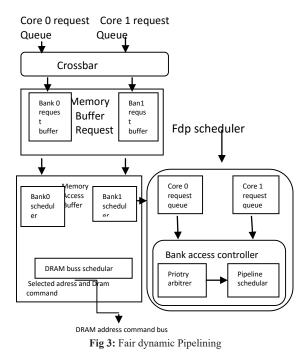

In this research our focus is to solve complications just like undernourishment, complication, along with unknown DRAM admittance latency, many of us existing the DRAM admittance operations structure Sensible Active Pipelining (FDP) ram admittance arranging with a couple important characteristics. In multi-core systems, almost all cores discuss the DRAM bandwidth causes it to be turn into a vital distributed learning resource. Evaluations with different common strategies revealed which our objects operations is usually prevalent inside spatial along with temporary factors about ram parallel admittance effectiveness along with prices a smaller amount space for storing to prepare objects when compared with URL set up thing firm. Many of us existing Hierarchical Propagated Memory space (HSM) structure that may be hierarchically constructed ram distributed through multi-cores. The particular test consequence revealed which the FDP arranging helps make the bandwidth stocks to achieve sought after common latencies pertaining to variable cores ram accesses. A whole new moderately-broad mapping policy helpful to guide info amongst dissimilar amounts of accumulation along with ram, which encourages the consistency involving distributed ram. This report dependent on the recommended authentic scalable, triple- based multi-core structure offering equipment stage support pertaining to object-oriented system. Second, it offers a superior a alterable top precedence approach to help make the reply involving ram extra comparatively. Along with a fresh objects operations also recommended. 1st, the structure prevents sudden lengthy latencies or maybe undernourishment involving ram asks for when using the dynamic pipeline design policy.

Keywords: Memory hierarchy, object mapping, object management, cache mapping

## **INTRODUCTION**

Subject Focused development has become come about along with adopted inside very last 2 decades because abstraction, management, reusability along with cost effective qualities; Ram management service pertaining to OO software programs on operating system amount is often a new measurement containing recently been purposed in addition to productive recollection management on multi primary architectures can be researched with this investigation papers [4]. OO features inherit attributes pertaining to concurrency because a number of objects make a modern by participating jointly, many can certainly work at home to help carry out his or her jobs, many wants synchronization.

In the event that energy involving processor can be improving explanatory versus recollection energy with regards to gain access to time along with music group width improving linearly its 6 rates 1 each and every year or two season [7] .Therefore despite the fact that an extremely productive recollection management structure has become purposed with this investigation papers "Memory Wall" [6] still prevails. Within this papers recollection management method has become purposed on each components along with software conclude, with this investigation papers recollection management structure can be purposed for the multi-core structures referred to as TriBA, [11] this is a multi-core structures purposed inside investigation containing recently been discovered really productive. With TriBA each primary referred to as any cell phone, each cell phone is often a comprehensive PROCESSOR, a few tissues make a class,

in the class each and every cell phone can be connected to additional class pals / buddies straight, right now there any are generally a few groups along with each and every class can be attached together so that it helps make any nine primary model. TriBA absolutely tallies with the recollection management structure purposed with this papers.

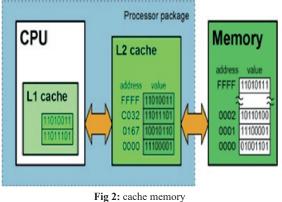

Although cell with team tend to be connected to each team spouse cell as well as all teams tend to be hooked up to one another nevertheless the inter key interconnection carries a constrained throughput so it's required to have efficient propagated recollection plan. Each and every cell features a number of bit rule variety designated to it, a couple most crucial portions details the actual team NO. of an cell as well as a couple very least substantial portions details key variety inside of team. There's L1 cache related to each cell it is individual cache with the cell, L2 will be propagated one of several team. In this paper recollection administration in some measure inclusive mapping plan have been chosen consequently L2 will be subdivided with a number of areas a single element per participant cell and something element will be team public [14]. Next level or perhaps L3 would be the principal recollection additionally it is mapped in some measure inclusively. It is usually subdivided with a number of areas, each team carries an element between a number of and something element will be global public. Dimensions of all these kinds of areas tend to be configurable. Just about every team element with L3 will be additionally subdivided with some areas comparable to L2 individual areas and also a team public element.

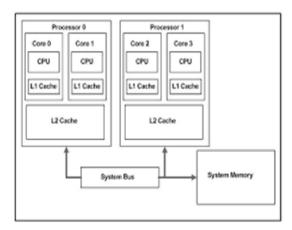

Fig 1: Multi-core architecture

### **HSMS: (Hierarchical Shared Memory System)**

In multi-core architecture nine cores are used each core done its own work these cores are inter linked with each other on a chip becomes the holdup of performance. CMP provide the facility cores to interconnect with each other on a network. Throughput of network slow down and not given the high efficient memory system which is required. HSM (Hierarchical Shared Memory) provide us a special system TriBA. System has three level of memory L1, L2 and L3. [14]

- Local cache

- · Shared memory

- · Main memory

### State of the Art:

Within this analysis strong object approaching is backed from the technique layout. There exists Item Platforms (OT) within electronics to support that plan. It's a selection, indexed by means of object amount, gain access to the object a search is manufactured within OT; [15] [16] you can find 3 sorts of object furniture within technique, personal, party community and also worldwide community object furniture. L1 holds personal object desk, L2 holds party community object desk, you can find 3 added bits within each accessibility within party community object furniture which usually informs that the object is distributed to which usually cell phone additionally the grubby bit is related to each accessibility. A new grubby object is not seen by means of some other party member. International community object desk rests within L3; gleam bit vector within each object accessibility which usually details the actual cell phone figures

discussing this kind of object. Item furniture are widely-used in this address plan to be able to translate exclusive address in to bodily details.

Subject variety is usually 20 or so tad thus final number connected with objects that may live in the system tend to be two hundred and twenty that's not just an adequate count within a working technique. Subject variety tend to be assigned throughout growing purchase you will find there's reuse bunch is employed from the technique and when the thing is usually compiled by simply trash collector its variety is usually forced in to bunch and its particular soiled tad is defined. While there is merely one area in which the thing referrals is usually located, most referrals tend to be invalidated by simply this action. When obtain completely new thing is made the thing variety is employed via reuse bunch by simply this plan technique copes with to own adequate thing count.

### **Object Number Allocation:**

In object oriented system everything which has an object a object id, and object reference that's create OT according to its category. Every object has a specific number and OT entry and run its own time. The object number is organized in array which is increased orderly and destroy object store in recycle.

# **EXPERIMENTAL ANALYSIS**

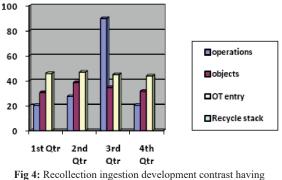

We have developed the objects management machine in C++ associate in nursing this simulation program carries out an event-driven simulation that describe the method of object variety allocation and use with many alterable parameters. Furthermore, some manually generated benchmarks are used to test the performance of our style. We have a tendency to investigate some of the java programs by traces obtained from a changed jvm. During this experiment we have a tendency to use Sun's java2 software. Normal Edition, 1. 3. 1 01. Because the experiment platform. By using the training looking up power associated with JVM in addition to JVMPI, gathered the thing development, subject admittance in addition to subject eliminate occasions for each and every java applications. Individuals operations need subject administration for you to a sign or even de-allocation subject assortment in addition to subject table access. Target guide, subject dimension in addition to admittance counteract are extremely logged inside a sketch record.

The particular criteria as well as plans are generally constructed to own with predictor method so that you can collect the initial effecting behaviour with no hotspot's amendment [19]. The particular plans currently being examined incorporate Z . ranking, N get married, Xcessos, Judith, Arons, N deliver, as well as Smaller DB are generally totally free as well as open-source espresso program related to browsing the internet. It is currently being published by some form of staff regarding installers serious about seeing a great screen created for using the companies involving XML files.

Table 1: The Simulation Results Of The Object Operations

| Bench mark | operations | objects | OT entry | Recycle stack |

|------------|------------|---------|----------|---------------|

| Z score    | 52830013   | 2444666 | 507313   | 299101        |

| J marry    | 68999587   | 2061148 | 98631    | 47610         |

| Xcessos    | 35990462   | 1611361 | 203570   | 52278         |

| Judith     | 24701542   | 1271872 | 226035   | 61252         |

| Arsons     | 27991014   | 167042  | 72212    | 20836         |

| J ship     | 27991014   | 28288   | 28288    | 0             |

| Small DB   | 54081      | 14582   | 14582    | 0             |

In table I, we demonstrate the recreation consequences of the object procedures whenever running benchmarks. The results include the amount of object procedures, items, object stand synonyms and reuse stack objects while applying our object operations element. We make sure that we require less entries of object table then the overall number of objects below the issue involving sells collection in the interest of keeping OT entries The object range pieces choose the particular maximal number of things could located inside object table. Take software Address for example, there are 2815251 operations upon 167042 physical objects and also allotted 72212 target stand records to avoid wasting the information. Concurrently, 20836 recycled target amount saved within the recycling collection. Due to the fact there are absolutely no damage operate within standard, L send, Arons and also little DB, the recycling collection is 0 and also the target stand sizing is equal to the volume of physical objects. It's apparent of which, on account of trying to recycle the utilized invalid target amount, less completely new target stand access ought to be initialized which make it's possible to budget for a smaller memory space intended for target stand. Moreover, 20 parts target amount may distinguish more than two hundred and twenty physical objects by means of trying to recycle within the whole runtime.

hyperlink organised target table

Concerning the spatial expense, given that each and every OT accessibility is usually sixty-four pieces in addition to 20 pieces recycled subject variety stashed in recycle pile, the entire storage desired is usually subject dining room table sizing in addition recycle pile sizing. In web page link architecture, OT accessibility is additionally sixty-four pieces in addition to subject variety doesn't need to have stashed as the listing however future accessibility deal with ordered to provide to avoid wasting [18]. Your memory space area expense contrast among our own methods (above) along with web page link architecture (nether) of those 8 benchmarks is usually shown in Determine graph. It may be witnessed our methods take up smaller sized storage when compared with standard linked subject dining room table. This is due to, similarly, this recycle pile merely retail store this subject variety rather than the full OT accessibility; for the different palm, lets recycle this sick object's OT records may prevent generate additional new OT records. The reason why regarding they have got this similar expense in Jship, Arson in addition to smallDB is there are zero wrecked subject in individuals packages in addition to our own recycle technique doesn't function. Reuse pile is really a contingency collector, hence subject formation is being conducted even though wrecked subject is usually cost-free its OT accessibility. For this reason planned scheme offers increased memory space operation when compared with standard linked organized subject dining room table. Inside stage regarding temporary, regarding subject portion, two memory space says had to glimpse this rank and find the superior piece on the recycle pile, and one memory space write should be performed to change the brand new object's OT accessibility content material such as set this good little bit. Furthermore, merely two memory space creates should be used regarding subject deletion: set this good little bit inside OT accessibility in addition to drive sick subject variety into recycle pile. Any time rubbish series in addition to memory space compaction started out, cost-free memory space facts can be had by simply check this sick subject variety in recycle pile in addition to lookup individuals matching OT accessibility. That will helps this rubbish series and can not necessarily impact the thing variety lets recycle practice. Waste series algorithms relate [18]. We've got formulated this Good Vibrant Pipelining Scheduler simulator in C++. Your packages currently being assessed include bzip, gcc, six pack in addition to swimming. We all use the know on the memory space access request of these packages while benchmarks.

### Results

Memory space is contributed source among many study course in addition to improper use as well as unfair sharing could potentially cause critical issues for technique overall performance. To talk about storage correctly among many cores Fair Active Pipelining (FDP) have been purposed on this document, there'll be a new FDP scheduler inside the technique which often mange the storage accessibility needs. It will are comes after there are D cores inside a technique there'll be T storage finance institutions inside the technique, each standard bank may sustain a new queue for every core which can be requesting storage accessibility, there'll be first focus for every queue, if a request from your queue will likely be complies with the goal will likely be made absolutely no (lowest) the other will likely be additional with goal involving additional queues. As soon as there'll be absolutely no request from your core the queue will likely be deleted from standard bank. This system is better than traditional pooling system through which each and every core is provided never-ending cycle actually the item doesn't possess a ask storage accessibility.

## CONCLUSIONS

Trials results display until this completely new subject operations structure can significantly enhance the particular ram by using object-oriented packages along with the FDP booking tends to make the particular bandwidth gives you to achieve wanted average latencies intended for variable cores ram accesses. A new subject operations type can be introduced, which use subject table in addition to delete pile structure to facilitate specific vibrant subject operations. With regard to manage discuss ram involving cores successfully; we check out any hierarchical propagated ram technique using the services of the particular partially-inclusive cache mapping coverage. This cardstock planned the latest subject operations type to supply good performance ram operations of multi- key.

## REFERENCES

[1] Kunle Olukotun, Lance Hammond, and James Laudon, "Chip Multiprocessor Architecture: Techniques to Improve Throughput and Latency," Morgan & Claypool Publishers.

[2] Tran, V.D., Hluchy, L., Nguyen, G.T., 2000 "Parallel programming with data driven model," 8th Euromicor Workshop on Parallel and Distributed Processing, IEEE Computer Society Press, Greece, Jan, pp. 205-211.

[3] Schwan, K., Ramnath, R., Vasudevan, S., Ogle, D., Apr 1988, "A language and system for the construction and tuning of parallel programs," IEEE Transactions on Software Engineering, pp. 455 – 471.

[4] PATTERSON, DAVID, ET AL., (March/April 1997)," "A Case for Intelligent RAM. IEEE Micro," pp. 34-44.

[5] SAULSBURY, ASHLEY, PONG, FONG, AND NO-WATZYK, ANDREAS, (May 1996), "Missing the Memory Wall: The Case for Processor/Memory Integration," Proceedings of the International Symposium on Computer Architecture pp. 90-101.

[6] K. Asanovic, R. Bodik, B. C. Catanzaro et al, Dec. 18, 2006 "The Landscape of Parallel Computing Research: A View from Berkeley," Technical Report UCB/EECS-2006-183, EECS Department, University of California, Berkeley. [7] D. Burger, J. R. Goodman, and A. Kagi, New York, NY, USA, 1996. ACM Press "Memory bandwidth limitations of future microprocessors," Proceedings of the 23rd nual international symposium on Computer architecture, pages 78.89,.

[8] Scott Rixner, William J. Dally, Ujval J. Kapasi, Peter Mattson, and John D. Owens, 2000 "Memory access scheduling," ISCA-27.

[9] Feng SHI, Weixing JI, Baojun QIAO, Bin LIU, Haroon-ul-Rashid, ASAP'07, 2007, "A Triplet Based Computer Architecture Supporting Parallel Object Computing," pp. 192-197.

[10] Sivarama P. Dandamudi, 1990 "Hierarchical Interconnection Networks for Multicomputer Systems[J]," IEEE Transactions on Computers, 39(6): 786-797.

[11] Wang Zuo and Shi Feng et al, ACM Press, 2009: "N-Port Memory Mapping for LUT- Based FPGAs," The 17th ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA'09). Monterey, California: 279-279.

[12] R. Colwell, E. Gehringer, and E. Jensen, 1988, "Performance effects of architectural complexity in the intel 432," ACM Transactions on Computer Systems, pp. 296-339.

[13] Dieckmann S, Hölzle U, ECOOP'99, 1999, "A Study of the Allocation Behavior of the SPECjvm98 Java Benchmarks," pp. 92-115.

[14] Onur Mutlu , Thomas Moscibroda, December 01-05, 2007 "Stall-Time Fair Memory Access Scheduling for Chip Multiprocessors," Proceedings of the 40th Annual IEEE/ACM International Symposium on Microarchitecture, p.146-160,.

[15] Kim, S., Chandra, D., and Solihin, Y., (Sept. 29 – Oct. 03, 2004). "Fair Cache Sharing and Partitioning in a Chip Multiprocessor Architecture," Proc. of the 13th Intl.1 Conf. on Parallel Arch. and Compilation Techniques PACT '04. 111-122.

[16] K. J. Nesbit, N. Aggarwal, J. Laudon, and J. E. Smith. 2006, "Fair queuing memory systems," MICRO-39,.

[17] Lindho lm T, Yellin F., 1996 "The Java Virtual Machine Specification," Addison-Wesley, .

[18] Weixing Ji, Feng Shi, Baojun Qiao, ACM Press, 2007 "A Self-maintained Memory Module Supporting DMM," International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CAS-ES'07):189-197.

[19] Lindho lm T, Yellin F., 1996 "The Java Virtual Machine Specification," Addison-Wesley, .